### LAN8810/LAN8810i

# GMII 10/100/1000 Ethernet Transceiver with HP Auto-MDIX Support

### PRODUCT FEATURES

**Datasheet**

### **Highlights**

- Single-Chip Ethernet Physical Layer Transceiver (PHY)

- Compliant with IEEE 802.3ab (1000BASE-T), IEEE 802.3u (Fast Ethernet), and ISO 802-3/IEEE 802.3 (10BASE-T)

- HP Auto-MDIX support in accordance with IEEE 802.3ab specification at 10/100/1000 Mbps operation

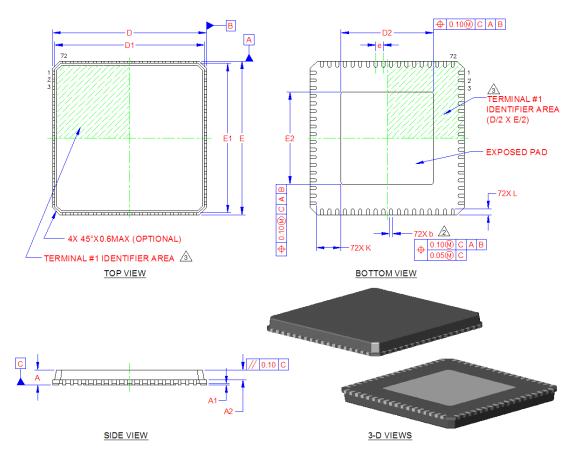

- Small footprint 72-pin QFN lead-free RoHS compliant package with GMII (10 x 10 x 0.9mm height)

- Flexible configurations for LED status indicators

- Implements Reduced Power Operating Modes

#### **Target Applications**

- Set-Top Boxes

- Networked Printers and Servers

- Test Instrumentation

- LAN on Motherboard

- Embedded Telecom Applications

- Video Record/Playback Systems

- Cable Modems/Routers

- DSL Modems/Routers

- Digital Video Recorders

- IP and Video Phones

- Wireless Access Points

- Digital Televisions

- Digital Media Adaptors/Servers

- Gaming Consoles

- POE Applications

### **Key Benefits**

- High-Performance 10/100/1000 Ethernet Transceiver

- Compliant with IEEE 802.3ab (1000BASE-T)

- Compliant with IEEE 802.3/802.3u (Fast Ethernet)

- Compliant with ISO 802-3/IEEE 802.3 (10BASE-T)

- 10BASE-T, 100BASE-TX and 1000BASE-T support

- Loop-back modes

- Auto-negotiation (NEXT page support)

- Automatic polarity detection and correction

- Link status change wake-up detection

- Vendor specific register functions

- Supports GMII interface

- Controlled impedance outputs

- Four status LED outputs and configurable LED modes with support for tricolor operation

- Compliant with IEEE 802.3-2005 standards

- GMII pins tolerant to 3.6V

- Integrated DSP implements adaptive equalizer, echo cancellers, and crosstalk cancellers

- Efficient digital baseline wander correction

- Power and I/Os

- Configurable LED outputs

- Various low power modes

- Variable voltage I/O supply (2.5V/3.3V)

- Miscellaneous Features

- IEEE 1149.1 (JTAG) boundary scan

- Multiple clock options 25MHz crystal or 125MHz clock

- Packaging

- 72-pin QFN (10x10 mm) lead-free RoHS compliant package with GMII

- Environmental

- Commercial temperature range (0°C to +70°C)

- Industrial temperature range (-40°C to +85°C)

#### **Order Numbers:**

LAN8810-AKZE for 72-pin, QFN lead-free RoHS compliant package (0 to +70°C temp range)

LAN8810i-AKZE for 72-pin, QFN lead-free RoHS compliant package (-40 to +85°C temp range)

This product meets the halogen maximum concentration values per IEC61249-2-21 For RoHS compliance and environmental information, please visit www.smsc.com/rohs

Please contact your SMSC sales representative for additional documentation related to this product such as application notes, anomaly sheets, and design guidelines.

Copyright © 2013 SMSC or its subsidiaries. All rights reserved.

Circuit diagrams and other information relating to SMSC products are included as a means of illustrating typical applications. Consequently, complete information sufficient for construction purposes is not necessarily given. Although the information has been checked and is believed to be accurate, no responsibility is assumed for inaccuracies. SMSC reserves the right to make changes to specifications and product descriptions at any time without notice. Contact your local SMSC sales office to obtain the latest specifications before placing your product order. The provision of this information does not convey to the purchaser of the described semiconductor devices any licenses under any patent rights or other intellectual property rights of SMSC or others. All sales are expressly conditional on your agreement to the terms and conditions of the most recently dated version of SMSC's standard Terms of Sale Agreement dated before the date of your order (the "Terms of Sale Agreement"). The product may contain design defects or errors known as anomalies which may cause the product's functions to deviate from published specifications. Anomaly sheets are available upon request. SMSC products are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of SMSC and further testing and/or modification will be fully at the risk of the customer. Copies of this document or other SMSC literature, as well as the Terms of Sale Agreement, may be obtained by visiting SMSC's website at http://www.smsc.com. SMSC is a registered trademark of Standard Microsystems Corporation ("SMSC"). Product names and company names are the trademarks of their respective holders.

The Microchip name and logo, and the Microchip logo are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT AND THE LIKE, AND ANY AND ALL WARRANTIES ARISING FROM ANY COURSE OF DEALING OR USAGE OF TRADE. IN NO EVENT SHALL SMSC BE LIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES; OR FOR LOST DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND; REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON CONTRACT; TORT; NEGLIGENCE OF SMSC OR OTHERS; STRICT LIABILITY; BREACH OF WARRANTY; OR OTHERWISE; WHETHER OR NOT ANY REMEDY OF BUYER IS HELD TO HAVE FAILED OF ITS ESSENTIAL PURPOSE, AND WHETHER OR NOT SMSC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

# **Table of Contents**

| <b>Chap</b> 1.1 |         | Introduction                                  |    |

|-----------------|---------|-----------------------------------------------|----|

| Chap            | ter 2   | Pin Description and Configuration             | 10 |

| 2.1             |         | Types                                         |    |

|                 | Dullei  | Types                                         | 10 |

| Chap            | ter 3   | Functional Description                        | 19 |

| 3.1             |         | egotiation                                    |    |

| J. 1            | 3.1.1   | Restarting Auto-negotiation                   |    |

|                 | 3.1.2   | Disabling Auto-negotiation.                   |    |

|                 | 3.1.2   | Parallel Detection                            |    |

|                 | 3.1.4   | Master/Slave                                  |    |

|                 | 3.1.5   | Manual Operation                              |    |

|                 | 3.1.6   | Half vs. Full-Duplex                          |    |

| 3.2             |         | to-MDIX                                       |    |

| 3.2             | 3.2.1   | Required Ethernet Magnetics                   |    |

| 2.2             | _       |                                               |    |

| 3.3             |         | nterface                                      |    |

| 2.4             | 3.3.1   | MII Isolate Mode                              |    |

| 3.4             |         | Management Interface (SMI)                    |    |

| 3.5             |         | pt Management                                 |    |

| 3.6             |         | S                                             |    |

|                 | 3.6.1   | Hardware Reset (nRESET)                       |    |

|                 | 3.6.2   | Software Reset                                |    |

|                 | 3.6.3   | Power-Down Reset                              |    |

| 3.7             |         | -Down modes                                   |    |

|                 | 3.7.1   | General Power-Down                            |    |

|                 | 3.7.2   | Energy Detect Power-Down                      |    |

|                 | 3.7.3   | Hardware Power-Down                           |    |

| 3.8             |         | uration                                       |    |

|                 | 3.8.1   | Hardware Configuration                        |    |

|                 | 3.8.2   | Software Configuration                        |    |

| 3.9             |         | laneous Functions                             |    |

|                 | 3.9.1   | LEDs                                          |    |

|                 | 3.9.2   | Variable Voltage I/O                          |    |

|                 | 3.9.3   | Isolate Mode                                  |    |

|                 | 3.9.4   | Carrier Sense                                 |    |

|                 | 3.9.5   | Collision Detect                              | 36 |

|                 | 3.9.6   | Link Integrity                                | 36 |

|                 | 3.9.7   | Speed Optimizer                               | 38 |

|                 | 3.9.8   | Loopback Operation                            |    |

|                 | 3.9.9   | IEEE 1149.1 (JTAG) Boundary Scan              | 39 |

|                 | 3.9.10  | Advanced Features                             | 39 |

| 3.10            | Applica | ation Diagrams                                | 41 |

|                 | 3.10.1  | Simplified Application Diagram                | 41 |

|                 | 3.10.2  | Power Supply & Twisted Pair Interface Diagram | 42 |

|                 |         |                                               |    |

| Chap            | ter 4   | Register Descriptions                         | 43 |

| 4.1             | Regist  | er Nomenclature                               |    |

| 4.2             | -       | y PHY Registers                               |    |

|                 | 4.2.1   | Basic Control Register                        |    |

|                 | 4.2.2   | Basic Status Register                         |    |

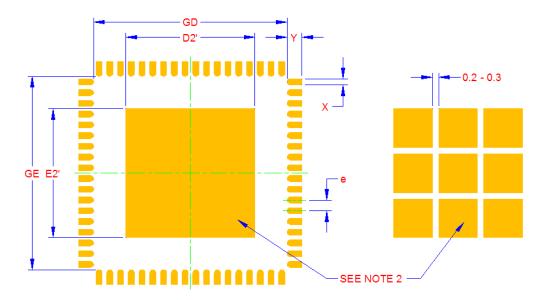

| Char | ntor 6 L         | ackage ( hitline                                 | U×   |

|------|------------------|--------------------------------------------------|------|

|      |                  | Package Outline                                  | 00   |

| 5.6  | Clock Ci         | rcuit                                            | . 97 |

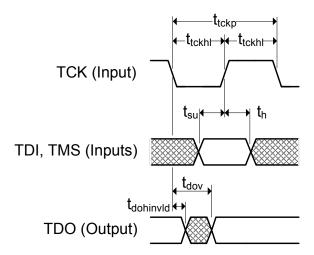

|      | 5.5.8            | JTAG Timing                                      |      |

|      | 5.5.7            | SMI Timing                                       |      |

|      | 5.5.6            | MII Timing (100BASE-TX, 10BASE-T)                |      |

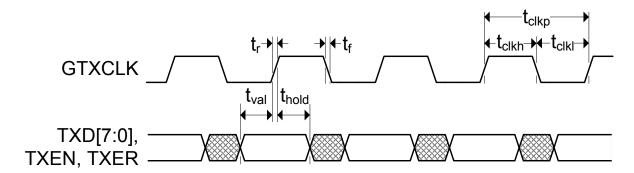

|      | 5.5.5            | GMII Timing (1000BASE-T)                         |      |

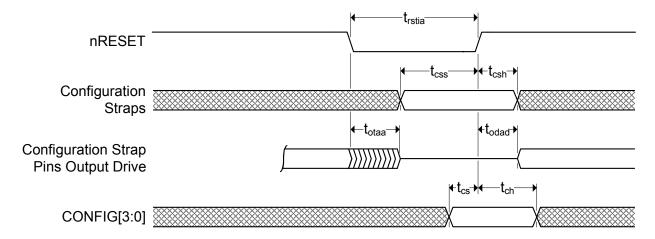

|      | 5.5.4            | Reset Timing                                     |      |

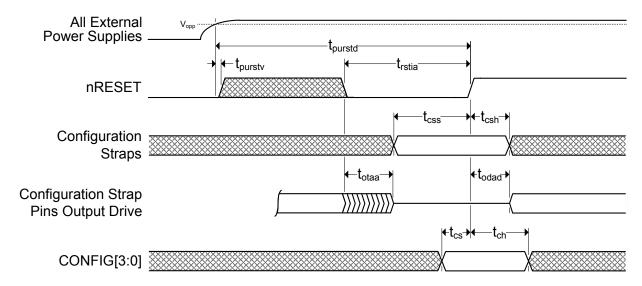

|      | 5.5.3            | Power-On Reset Timing                            |      |

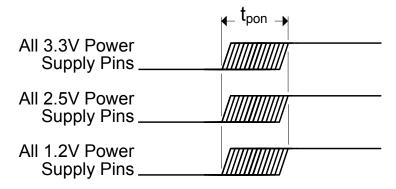

|      | 5.5.2            | Power Sequence Timing                            |      |

|      | 5.5.1            | Equivalent Test Load                             |      |

| 5.5  | •                | cifications                                      |      |

| 5.4  |                  | cifications                                      |      |

| 5.3  |                  | onsumption                                       |      |

| 5.2  | •                | g Conditions**                                   |      |

| 5.1  |                  | Maximum Ratings*                                 |      |

| -    |                  | •                                                |      |

| Char | oter 5 (         | Operational Characteristics                      | QΊ   |

|      | 4.3.14           | Transmit Packet Counter Low Register             | . ŏ1 |

|      | 4.3.13           | Transmit Packet Counter Mid Register             |      |

|      | 4.3.12<br>4.3.13 | Transmit Packet Counter High Register            |      |

|      | 4.3.11           | Receive Error During Idle Counter Register       |      |

|      | 4.3.10<br>4.3.11 | Receive Error During Data Counter Register       |      |

|      | 4.3.9<br>4.3.10  |                                                  |      |

|      | 4.3.9            | CRC Error Counter Low Register                   |      |

|      | 4.3.8            | CRC Error Counter Mid Register                   |      |

|      | 4.3.7            | CRC Error Counter High Register                  |      |

|      | 4.3.6            | Receive Error-Free Packets Counter Low Register  |      |

|      | 4.3.4            | Receive Error-Free Packets Counter Mid Register  |      |

|      | 4.3.4            | Receive Error-Free Packets Counter High Register |      |

|      | 4.3.3            | User Status 2 Register                           |      |

|      | 4.3.1            | User Status 1 Register                           |      |

| 1.0  | 4.3.1            | Advanced Register Mapping                        |      |

| 4.3  |                  | d PHY Registers                                  |      |

|      | 4.2.22           | PHY Special Control / Status Register            |      |

|      | 4.2.21           | Interrupt Mask Register                          |      |

|      | 4.2.20           | Interrupt Source Flags Register                  |      |

|      | 4.2.19           | Control / Status Indications Register            |      |

|      | 4.2.18           | Advanced Register Read Data Port                 |      |

|      | 4.2.17           | Advanced Register Address Port                   |      |

|      | 4.2.16           | Extended Mode Control/Status Register            |      |

|      | 4.2.15           | 10/100 Special Modes Register                    |      |

|      | 4.2.14           | 10/100 Mode Control/Status Register              |      |

|      | 4.2.13           | Link Control Register                            |      |

|      | 4.2.12           | Extended Status Register                         |      |

|      | 4.2.11           | Master/Slave Status Register                     |      |

|      | 4.2.10           | Master/Slave Control Register                    |      |

|      | 4.2.9            | Auto Negotiation Next Page RX Register           |      |

|      | 4.2.8            | Auto Negotiation Next Page TX Register           |      |

|      | 4.2.7            | Auto Negotiation Expansion Register              |      |

|      | 4.2.6            | Auto Negotiation Link Partner Ability Register   |      |

|      | 4.2.5            | Auto Negotiation Advertisement Register          |      |

|      | 4.2.4            | PHY Identifier 2 Register                        |      |

|      | 4.2.3            | PHY Identifier 1 Register                        | . 47 |

| Chanter 7 | Datasheet Revision | History | 100 |

|-----------|--------------------|---------|-----|

| Chapter / |                    |         |     |

# **List of Figures**

| Figure 1.1  | Internal Block Diagram                                              | 8  |

|-------------|---------------------------------------------------------------------|----|

| Figure 1.2  | System Level Block Diagram                                          |    |

| Figure 2.1  | 72-QFN Pin Assignments (TOP VIEW)                                   |    |

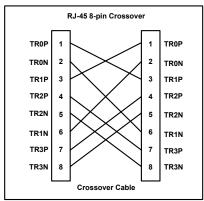

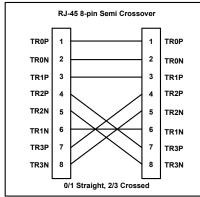

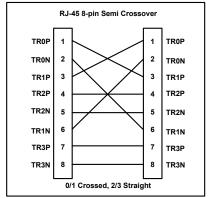

| Figure 3.1  | Cable Connection Types: Straight-Through, Crossover, Semi Crossover | 23 |

| Figure 3.1  | MDIO Timing and Frame Structure - READ Cycle                        | 25 |

| Figure 3.2  | MDIO Timing and Frame Structure - WRITE Cycle                       | 25 |

| Figure 3.1  | Simplified Application Diagram                                      |    |

| Figure 3.2  | Power Supply & Twisted Pair Interface Diagram                       |    |

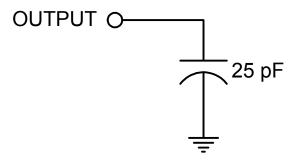

| Figure 5.1  | Output Equivalent Test Load                                         | 87 |

| Figure 5.2  | Power Sequence Timing                                               | 88 |

| Figure 5.3  | Power-On Reset Timing                                               | 89 |

| Figure 5.4  | Reset Timing                                                        | 90 |

| Figure 5.5  | GMII Transmit Timing                                                | 91 |

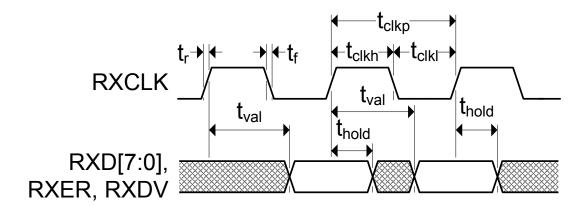

| Figure 5.6  | GMII Receive Timing                                                 | 92 |

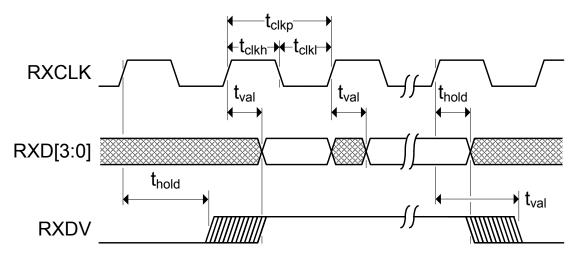

| Figure 5.7  | MII Receive Timing                                                  | 93 |

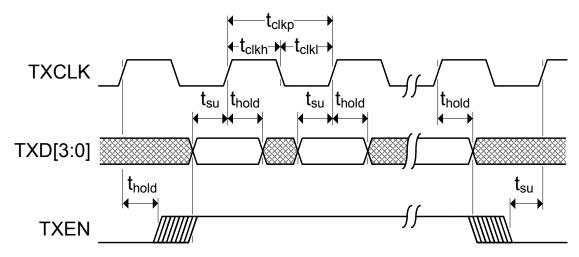

| Figure 5.8  | MII Transmit Timing                                                 | 94 |

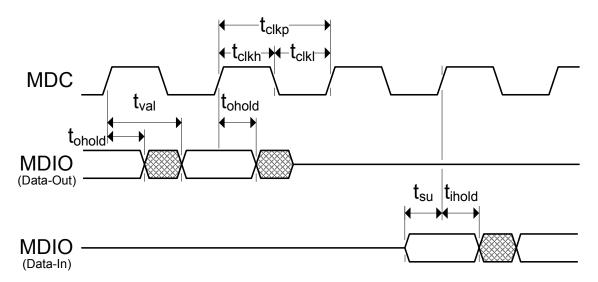

| Figure 5.9  | SMI Timing                                                          | 95 |

| Figure 5.10 | JTAG Timing                                                         | 96 |

| Figure 6.1  | 72-QFN Package                                                      | 98 |

| Figure 6.2  | 72-QFN Recommended PCB Land Pattern                                 | 99 |

# **List of Tables**

|            | GMII Interface Pins                                          |       |

|------------|--------------------------------------------------------------|-------|

|            | Serial Management Interface (SMI) Pins                       |       |

| Table 2.3  | LED & Configuration Pins                                     | 13    |

| Table 2.4  | Ethernet Pins                                                | 14    |

| Table 2.5  | JTAG Pins                                                    | 15    |

| Table 2.6  | Miscellaneous Pins                                           | 15    |

|            | Power Pins                                                   |       |

| Table 2.8  | 72-QFN Pin Assignments                                       | 17    |

| Table 2.9  | Buffer Types                                                 | 18    |

| Table 3.1  | Master/Slave Resolution for 1000BASE-T                       | 21    |

| Table 3.2  | CRS Behavior                                                 | 22    |

| Table 3.3  | GMII/MII Signal Mapping                                      | 24    |

| Table 3.4  | Interrupt Management Table                                   | 26    |

| Table 3.5  | Configuration Straps                                         | 29    |

| Table 3.6  | Hardware Connection Determines Configuration Pin Value (CPV) | 30    |

|            | SMI Address Configuration with PAUSE=0                       |       |

|            | SMI Address Configuration with PAUSE=1                       |       |

| Table 3.9  | Configuring the Mode of Operation with MACCLKDIS=0           | 32    |

|            | Configuring the Mode of Operation with MACCLKDIS=1           |       |

|            | Register Bits Impacted by the Mode of Operation (MOD)        |       |

|            | LED Mode 1 Operation - LED_MODE[1:0]=01b                     |       |

|            | LED Mode 2 Operation - LED_MODE[1:0]=10b                     |       |

|            | LED Mode 3 Operation - LED_MODE[1:0]=11b                     |       |

|            | IEEE 1149.1 Op Codes                                         |       |

|            | Register Bit Types                                           |       |

|            | PHY Control and Status Registers                             |       |

|            | Advanced Register Mapping                                    |       |

|            | Power Consumption - 1000BASE-T Linked                        |       |

|            | Power Consumption - 100BASE-TX Linked                        |       |

| Table 5.3  | Power Consumption - 10BASE-T Linked                          | 84    |

| Table 5.4  | Power Consumption - Energy Detect                            | 84    |

|            | Power Consumption - Hardware Power Down (PLL Enabled)        |       |

|            | Power Consumption - Hardware Power Down (PLL Disabled)       |       |

| Table 5.7  | I/O Buffer Characteristics                                   | 85    |

| Table 5.8  | 1000BASE-T Transceiver Characteristics                       | 86    |

| Table 5.9  | 100BASE-TX Transceiver Characteristics                       | 86    |

| Table 5.10 | 10BASE-T Transceiver Characteristics                         | 86    |

| Table 5.11 | Power Sequence Timing Values                                 | 88    |

| Table 5.12 | Power-On Reset Timing Values                                 | 89    |

| Table 5.13 | Reset Timing Values                                          | 90    |

| Table 5.14 | GMII Transmit Timing Values                                  | 91    |

| Table 5.15 | GMII Receive Timing Values                                   | 92    |

|            | MII Receive Timing Values                                    |       |

| Table 5.17 | MII Transmit Timing Values                                   | 94    |

| Table 5.18 | SMI Timing Values                                            | 95    |

| Table 5.19 | JTAG Timing Values                                           | 96    |

| Table 5.20 | Crystal Specifications                                       | 97    |

|            | 72-QFN Dimensions                                            |       |

| Table 7.1  | Customer Revision History                                    | . 100 |

|            |                                                              |       |

# **Chapter 1 Introduction**

### 1.1 General Description

The SMSC LAN8810/LAN8810i is a low-power 10BASE-T/100BASE-TX/1000BASE-T Gigabit Ethernet physical layer (PHY) transceiver with variable I/O voltage that is fully compliant with the IEEE 802.3 and 802.3ab standards.

The LAN8810/LAN8810i can be configured to communicate with an Ethernet MAC via the standard MII(IEEE 802.3u)/GMII(IEEE 802.3z) interfaces. It contains a full-duplex transceiver for 1000Mbps operation on four pairs of category 5 or better balanced twisted pair cable. Per IEEE 802.3-2005 standards, all digital interface pins are tolerant to 3.6V.

The LAN8810/LAN8810i is configurable via hardware and software, supporting both IEEE 802.3-2005 compliant and vendor-specific register functions via SMI. The LAN8810/LAN8810i implements Auto-Negotiation to automatically determine the best possible speed and duplex mode of operation. HP Auto-MDIX support allows the use of direct connect or cross-over cables.

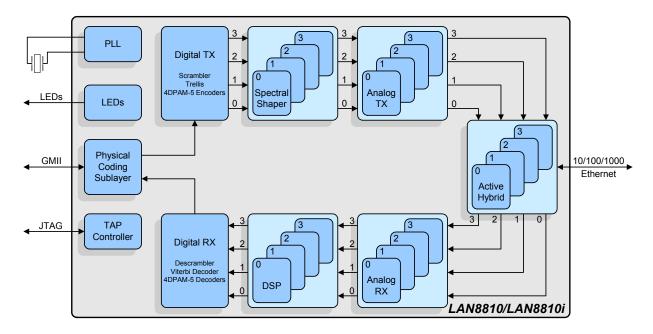

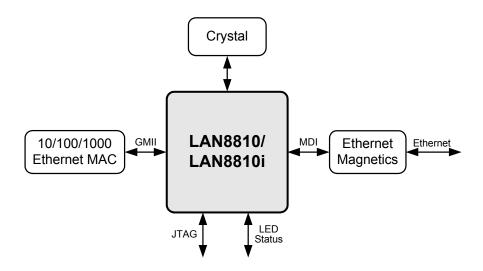

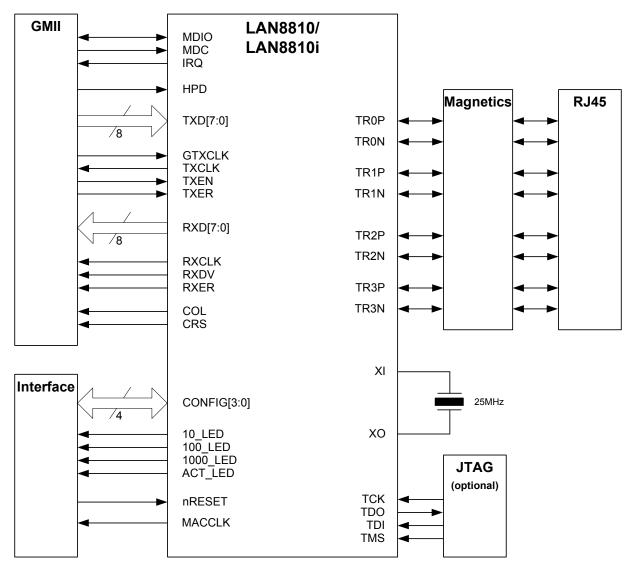

An internal block diagram of the LAN8810/LAN8810i is shown in Figure 1.1. A typical system-level diagram is shown in Figure 1.2.

Figure 1.1 Internal Block Diagram

Figure 1.2 System Level Block Diagram

# **Chapter 2 Pin Description and Configuration**

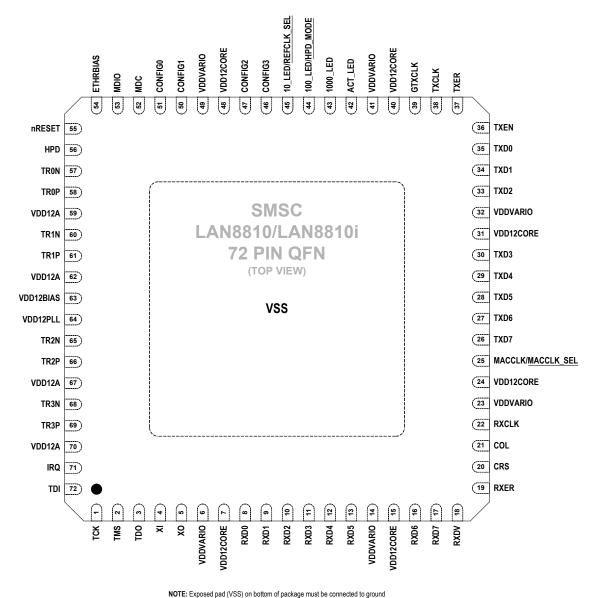

NOTE. Exposed pad (VSS) on bottom of package must be connected to ground

Figure 2.1 72-QFN Pin Assignments (TOP VIEW)

**Table 2.1 GMII Interface Pins**

| NUM<br>PINS | NAME                   | SYMBOL | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                |

|-------------|------------------------|--------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | Transmit Data 0        | TXD0   | VIS<br>(PD)    | The MAC transmits data to the PHY using this signal.                                                                                                                                                       |

| 1           | Transmit Data 1        | TXD1   | VIS<br>(PD)    | The MAC transmits data to the PHY using this signal.                                                                                                                                                       |

| 1           | Transmit Data 2        | TXD2   | VIS<br>(PD)    | The MAC transmits data to the PHY using this signal.                                                                                                                                                       |

| 1           | Transmit Data 3        | TXD3   | VIS<br>(PD)    | The MAC transmits data to the PHY using this signal.                                                                                                                                                       |

| 1           | Transmit Data 4        | TXD4   | VIS<br>(PD)    | The MAC transmits data to the PHY using this signal.                                                                                                                                                       |

| 1           | Transmit Data 5        | TXD5   | VIS<br>(PD)    | The MAC transmits data to the PHY using this signal.                                                                                                                                                       |

| 1           | Transmit Data 6        | TXD6   | VIS<br>(PD)    | The MAC transmits data to the PHY using this signal.                                                                                                                                                       |

| 1           | Transmit Data 7        | TXD7   | VIS<br>(PD)    | The MAC transmits data to the PHY using this signal.                                                                                                                                                       |

| 1           | Transmit Error         | TXER   | VIS<br>(PD)    | Indicates a transmit error condition.  Note: This input is ignored during 10BASE-T operation.                                                                                                              |

| 1           | Transmit Enable        | TXEN   | VIS<br>(PD)    | Indicates the presence of valid data on TXD[7:0]                                                                                                                                                           |

| 1           | Transmit Clock         | TXCLK  | VO8            | Used to latch data from the MAC into the PHY.  MII (100BASE-TX): 25MHz MII (10BASE-T): 2.5MHz  Note: For 1000BASE-T operation, GTXCLK is used as the transmit clock. TXCLK is not used in 1000BASE-T mode. |

| 1           | GMII Transmit<br>Clock | GTXCLK | VIS<br>(PD)    | 125MHz clock used to latch data from the MAC into the PHY in 1000BASE-T mode.                                                                                                                              |

| 1           | Receive Data 0         | RXD0   | VO6            | The PHY transfers data to the MAC using this signal.                                                                                                                                                       |

| 1           | Receive Data 1         | RXD1   | VO6            | The PHY transfers data to the MAC using this signal.                                                                                                                                                       |

| 1           | Receive Data 2         | RXD2   | VO6            | The PHY transfers data to the MAC using this signal.                                                                                                                                                       |

| 1           | Receive Data 3         | RXD3   | VO6            | The PHY transfers data to the MAC using this signal.                                                                                                                                                       |

| 1           | Receive Data 4         | RXD4   | VO6            | The PHY transfers data to the MAC using this signal.                                                                                                                                                       |

| 1           | Receive Data 5         | RXD5   | VO6            | The PHY transfers data to the MAC using this signal.                                                                                                                                                       |

Table 2.1 GMII Interface Pins (continued)

| NUM<br>PINS | NAME                                                       | SYMBOL     | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                                        |

|-------------|------------------------------------------------------------|------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | Receive Data 6                                             | RXD6       | VO6            | The PHY transfers data to the MAC using this signal.                                                                                                                                                                               |

| 1           | Receive Data 7                                             | RXD7       | VO6            | The PHY transfers data to the MAC using this signal.                                                                                                                                                                               |

| 1           | Receive Data<br>Valid                                      | RXDV       | VO6            | Indicates that recovered and decoded data is being presented on the receive data pins.                                                                                                                                             |

| 1           | Receive Error                                              | RXER       | VO6            | Asserted to indicate an error has been detected in the frame presently being transferred from the PHY.                                                                                                                             |

|             | Receive Clock                                              | RXCLK      | VO6            | Used to transfer data to the MAC.                                                                                                                                                                                                  |

| 1           |                                                            |            |                | GMII (1000BASE-T): 125MHz<br>MII (100BASE-TX): 25MHz<br>MII (10BASE-T): 2.5MHz                                                                                                                                                     |

| 1           | Collision Detect                                           | COL        | VO6            | Asserted to indicate detection of a collision condition. (used in half-duplex mode only)                                                                                                                                           |

| 1           | Carrier Sense                                              | CRS        | VO6            | Indicates detection of carrier. (used in half-duplex mode only)                                                                                                                                                                    |

|             | MAC Transmit<br>Clock                                      | MACCLK     | VO6            | 125MHz or 25MHz selectable MAC clock output as required by clause 40.6.1.2.5 of the IEEE 802.3ab specification.                                                                                                                    |

| 1           | MAC Clock<br>Frequency<br>Select<br>Configuration<br>Strap | MACCLK_SEL | VIS<br>(PD)    | This configuration strap is used to select the output frequency of MACCLK. When pulled-up to VDDVARIO, 25MHz is selected. When pulled-down to VSS, 125MHz is selected.  See Note 2.1 for more information on configuration straps. |

Note 2.1 Configuration strap values are latched on hardware reset. Configuration straps are identified by an underlined symbol name. Signals that function as configuration straps must be augmented with an external resistor when connected to a load. Refer to Section 3.8, "Configuration," on page 29 for additional information.

Table 2.2 Serial Management Interface (SMI) Pins

| NUM<br>PINS | NAME                     | SYMBOL | BUFFER<br>TYPE  | DESCRIPTION                                    |

|-------------|--------------------------|--------|-----------------|------------------------------------------------|

| 1           | SMI Clock                | MDC    | VIS<br>(PD)     | Serial Management Interface clock.             |

| 1           | SMI Data<br>Input/Output | MDIO   | VIS/VO8<br>(PU) | Serial Management Interface data input/output. |

Table 2.3 LED & Configuration Pins

| NUM<br>PINS | NAME                                                           | SYMBOL     | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                             |

|-------------|----------------------------------------------------------------|------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | 10BASE-T Link<br>LED Indicator                                 | 10_LED     | VO8            | 10BASE-T LED link indication. Refer to Section 3.9.1, "LEDs," on page 34 for additional information.                                                                                                                                                                                                                    |

| 1           | Reference<br>Clock Freq.<br>Select<br>Configuration<br>Strap   | REFCLK_SEL | VIS<br>(PD)    | This configuration strap is used to select the reference clock frequency. When pulled-up, a 125MHz reference clock is selected. When pulled-down, a 25MHz reference clock is selected.  See Note 2.2 for more information on configuration                                                                              |

|             |                                                                |            |                | straps.                                                                                                                                                                                                                                                                                                                 |

|             | 100BASE-TX<br>Link LED<br>Indicator                            | 100_LED    | VO8            | 100BASE-TX LED link indication. Refer to Section 3.9.1, "LEDs," on page 34 for additional information.                                                                                                                                                                                                                  |

| 1           | Hardware<br>Power Down<br>(HPD) Mode<br>Configuration<br>Strap | HPD_MODE   | VIS<br>(PD)    | This configuration strap is used to select the Hardware Power Down (HPD) mode. When pulledup, the PLL is not disabled when HPD is asserted. When pulled-down, the PLL is disabled when HPD is asserted.                                                                                                                 |

|             | ·                                                              |            |                | Refer to Section 3.7.3, "Hardware Power-Down," on page 28 for additional information.                                                                                                                                                                                                                                   |

|             |                                                                |            |                | See Note 2.2 for more information on configuration straps.                                                                                                                                                                                                                                                              |

| 1           | 1000BASE-T<br>Link LED<br>Indicator                            | 1000_LED   | VO8            | 1000BASE-T LED link indication. Refer to Section 3.9.1, "LEDs," on page 34 for additional information.                                                                                                                                                                                                                  |

| 1           | Link Activity<br>LED Indicator                                 | ACT_LED    | VO8            | Link activity LED indication. Refer to Section 3.9.1, "LEDs," on page 34 for additional information.                                                                                                                                                                                                                    |

| 1           | Configuration<br>Input 0                                       | CONFIG0    | VIS<br>(PD)    | This pin sets the PHYADD[1:0] bits of the 10/100 Special Modes Register on reset or power-up. It must be connected to VSS, 100_LED, 1000_LED, or VDDVARIO. Refer to Section 3.8.1.2, "CONFIG[3:0] Configuration Pins," on page 29 for additional information.                                                           |

| 1           | Configuration<br>Input 1                                       | CONFIG1    | VIS<br>(PD)    | This pin sets the PAUSE bit of the Auto Negotiation Advertisement Register and PHYADD [2] bit of the 10/100 Special Modes Register on reset or powerup. It must be connected to VSS, 100_LED, 1000_LED, or VDDVARIO. Refer to Section 3.8.1.2, "CONFIG[3:0] Configuration Pins," on page 29 for additional information. |

| 1           | Configuration<br>Input 2                                       | CONFIG2    | VIS<br>(PD)    | This pin sets the MOD[1:0] bits of the Extended Mode Control/Status Register on reset or power-up. It must be connected to VSS, 100_LED, 1000_LED, or VDDVARIO. Refer to Section 3.8.1.2, "CONFIG[3:0] Configuration Pins," on page 29 for additional information.                                                      |

| 1           | Configuration<br>Input 3                                       | CONFIG3    | VIS<br>(PD)    | This pin sets the CLK125DIS bit and MOD[3] bit of the Extended Mode Control/Status Register on reset or power-up. It must be connected to VSS, 100_LED, 1000_LED, or VDDVARIO. Refer to Section 3.8.1.2, "CONFIG[3:0] Configuration Pins," on page 29 for additional information.                                       |

Note 2.2 Configuration strap values are latched on hardware reset. Configuration straps are identified by an underlined symbol name. Signals that function as configuration straps must be augmented with an external resistor when connected to a load. Refer to Section 3.8, "Configuration," on page 29 for additional information.

**Table 2.4 Ethernet Pins**

| NUM PINS | NAME                                       | SYMBOL   | BUFFER<br>TYPE | DESCRIPTION                                                                                |

|----------|--------------------------------------------|----------|----------------|--------------------------------------------------------------------------------------------|

| 1        | Ethernet<br>TX/RX<br>Positive<br>Channel 0 | TR0P     | AIO            | Transmit/Receive Positive Channel 0.                                                       |

| 1        | Ethernet<br>TX/RX<br>Negative<br>Channel 0 | TR0N     | AIO            | Transmit/Receive Negative Channel 0.                                                       |

| 1        | Ethernet<br>TX/RX<br>Positive<br>Channel 1 | TR1P     | AIO            | Transmit/Receive Positive Channel 1.                                                       |

| 1        | Ethernet<br>TX/RX<br>Negative<br>Channel 1 | TR1N     | AIO            | Transmit/Receive Negative Channel 1.                                                       |

| 1        | Ethernet<br>TX/RX<br>Positive<br>Channel 2 | TR2P     | AIO            | Transmit/Receive Positive Channel 2.                                                       |

| 1        | Ethernet<br>TX/RX<br>Negative<br>Channel 2 | TR2N     | AIO            | Transmit/Receive Negative Channel 2.                                                       |

| 1        | Ethernet<br>TX/RX<br>Positive<br>Channel 3 | TR3P     | AIO            | Transmit/Receive Positive Channel 3.                                                       |

| 1        | Ethernet<br>TX/RX<br>Negative<br>Channel 3 | TR3N     | AIO            | Transmit/Receive Negative Channel 3.                                                       |

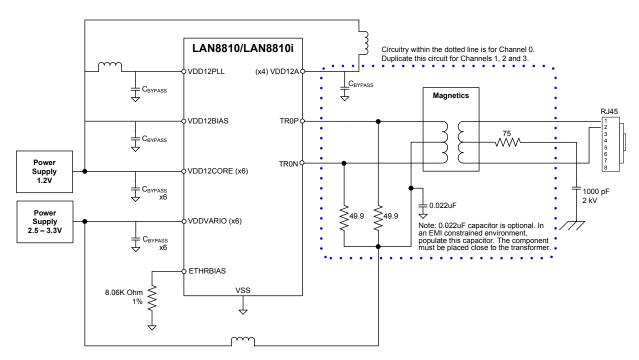

| 1        | External PHY<br>Bias Resistor              | ETHRBIAS | Al             | Used for the internal bias circuits. Connect to an external 8.06K 1.0% resistor to ground. |

### **Table 2.5 JTAG Pins**

| NUM PINS | NAME                     | SYMBOL | BUFFER<br>TYPE | DESCRIPTION                                                                          |

|----------|--------------------------|--------|----------------|--------------------------------------------------------------------------------------|

| 1        | JTAG Test<br>Data Out    | TDO    | VO8            | JTAG (IEEE 1149.1) data output.                                                      |

| 1        | JTAG Test<br>Data Input  | TDI    | VIS<br>(PU)    | JTAG (IEEE 1149.1) data input.  Note: When not used, tie this pin to VDDVARIO.       |

| 1        | JTAG Test<br>Clock       | TCK    | VIS<br>(PD)    | JTAG (IEEE 1149.1) test clock.  Note: When not used, tie this pin to VSS.            |

| 1        | JTAG Test<br>Mode Select | TMS    | VIS<br>(PU)    | JTAG (IEEE 1149.1) test mode select.  Note: When not used, tie this pin to VDDVARIO. |

### **Table 2.6 Miscellaneous Pins**

| NUM PINS | NAME                   | SYMBOL | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                          |

|----------|------------------------|--------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | Crystal Input          | ΧI     | ICLK           | External 25 MHz crystal input.                                                                                                                                       |

| 1        |                        |        |                | Note: This pin can also be driven by a single-<br>ended clock oscillator. When this<br>method is used, XO should be left<br>unconnected                              |

| 1        | Crystal<br>Output      | ХО     | OCLK           | External 25 MHz crystal output.                                                                                                                                      |

| 1        | System Reset           | nRESET | VIS<br>(PU)    | This active-low pin allows external hardware to reset the device.                                                                                                    |

| 1        | Interrupt<br>Request   | IRQ    | VO8            | Programmable interrupt request.  Note: When used, this pin requires an external 4.7K pull-up resistor.                                                               |

| 1        | Hardware<br>Power Down | HPD    | VIS<br>(PD)    | When asserted, this pin places the device into Hardware Power Down (HPD) mode. Refer to Section 3.7.3, "Hardware Power-Down," on page 28 for additional information. |

**Table 2.7 Power Pins**

| NUM PINS | NAME                                                                | SYMBOL    | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                         |

|----------|---------------------------------------------------------------------|-----------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6        | +3.3V/+2.5V<br>I/O Power<br>Supply Input                            | VDDVARIO  | Р              | +2.5V/+3.3V variable I/O power. Refer to Section 3.10, "Application Diagrams," on page 41 and the LAN8810/LAN8810i reference schematics for connection information. |

| 6        | Digital Core<br>+1.2V Power<br>Supply Input                         | VDD12CORE | Р              | Refer to Section 3.10, "Application Diagrams," on page 41 and the LAN8810/LAN8810i reference schematics for connection information.                                 |

| 4        | Ethernet<br>+1.2V Port<br>Power Supply<br>Input For<br>Channels 0-3 | VDD12A    | Р              | Refer to Section 3.10, "Application Diagrams," on page 41 and the LAN8810/LAN8810i reference schematics for connection information.                                 |

| 1        | Ethernet<br>+1.2V Bias<br>Power Supply<br>Input                     | VDD12BIAS | Р              | Refer to Section 3.10, "Application Diagrams," on page 41 and the LAN8810/LAN8810i reference schematics for connection information.                                 |

| 1        | Ethernet PLL<br>+1.2V Power<br>Supply Input                         | VDD12PLL  | Р              | Refer to Section 3.10, "Application Diagrams," on page 41 and the LAN8810/LAN8810i reference schematics for connection information.                                 |

| Note 2.3 | Ground                                                              | VSS       | Р              | Common Ground                                                                                                                                                       |

Note 2.3 Exposed pad on package bottom (Figure 2.1).

Table 2.8 72-QFN Pin Assignments

| PIN<br>NUM | PIN NAME                             | PIN<br>NUM | PIN NAME              | PIN<br>NUM | PIN NAME                    | PIN<br>NUM | PIN NAME  |

|------------|--------------------------------------|------------|-----------------------|------------|-----------------------------|------------|-----------|

| 1          | TCK                                  | 19         | RXER                  | 37         | TXER                        | 55         | nRESET    |

| 2          | TMS                                  | 20         | CRS                   | 38         | TXCLK                       | 56         | HPD       |

| 3          | TDO                                  | 21         | COL                   | 39         | GTXCLK                      | 57         | TR0N      |

| 4          | ΧI                                   | 22         | RXCLK                 | 40         | VDD12CORE                   | 58         | TR0P      |

| 5          | ХО                                   | 23         | VDDVARIO              | 41         | VDDVARIO                    | 59         | VDD12A    |

| 6          | VDDVARIO                             | 24         | VDD12CORE             | 42         | ACT_LED                     | 60         | TR1N      |

| 7          | VDD12CORE                            | 25         | MACCLK/<br>MACCLK_SEL | 43         | 1000_LED                    | 61         | TR1P      |

| 8          | RXD0                                 | 26         | TXD7                  | 44         | 100_LED/<br><u>HPD_MODE</u> | 62         | VDD12A    |

| 9          | RXD1                                 | 27         | TXD6                  | 45         | 10_LED/<br>REFCLK_SEL       | 63         | VDD12BIAS |

| 10         | RXD2                                 | 28         | TXD5                  | 46         | CONFIG3                     | 64         | VDD12PLL  |

| 11         | RXD3                                 | 29         | TXD4                  | 47         | CONFIG2                     | 65         | TR2N      |

| 12         | RXD4                                 | 30         | TXD3                  | 48         | VDD12CORE                   | 66         | TR2P      |

| 13         | RXD5                                 | 31         | VDD12CORE             | 49         | VDDVARIO                    | 67         | VDD12A    |

| 14         | VDDVARIO                             | 32         | VDDVARIO              | 50         | CONFIG1                     | 68         | TR3N      |

| 15         | VDD12CORE                            | 33         | TXD2                  | 51         | CONFIG0                     | 69         | TR3P      |

| 16         | RXD6                                 | 34         | TXD1                  | 52         | MDC                         | 70         | VDD12A    |

| 17         | RXD7                                 | 35         | TXD0                  | 53         | MDIO                        | 71         | IRQ       |

| 18         | RXDV                                 | 36         | TXEN                  | 54         | ETHRBIAS                    | 72         | TDI       |

|            | EXPOSED PAD MUST BE CONNECTED TO VSS |            |                       |            |                             |            |           |

MUST BE CONNECTED TO VSS

## 2.1 Buffer Types

**Table 2.9 Buffer Types**

| BUFFER TYPE | DESCRIPTION                                                                                                                                                                                                                                         |  |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| VIS         | Variable voltage Schmitt-triggered input                                                                                                                                                                                                            |  |  |  |

| VO6         | Variable voltage output with 6mA sink and 6mA source                                                                                                                                                                                                |  |  |  |

| VO8         | Variable voltage output with 8mA sink and 8mA source                                                                                                                                                                                                |  |  |  |

| PU          | 50uA (typical) internal pull-up. Unless otherwise noted in the pin description, internal pull-ups are always enabled.                                                                                                                               |  |  |  |

|             | <b>Note:</b> Internal pull-up resistors prevent unconnected inputs from floating. Do not rely on internal resistors to drive signals external to the device. When connected to a load that must be pulled high, an external resistor must be added. |  |  |  |

| PD          | 50uA (typical) internal pull-down. Unless otherwise noted in the pin description, internal pull-downs are always enabled.                                                                                                                           |  |  |  |

|             | Note: Internal pull-down resistors prevent unconnected inputs from floating. Do not rely on internal resistors to drive signals external to the device. When connected to a load that must be pulled low, an external resistor must be added.       |  |  |  |

| Al          | Analog input                                                                                                                                                                                                                                        |  |  |  |

| AIO         | Analog bi-directional                                                                                                                                                                                                                               |  |  |  |

| ICLK        | Crystal oscillator input pin                                                                                                                                                                                                                        |  |  |  |

| OCLK        | Crystal oscillator output pin                                                                                                                                                                                                                       |  |  |  |

| Р           | Power pin                                                                                                                                                                                                                                           |  |  |  |

**Note:** The digital signals are not 5V tolerant. Refer to Section 5.1, "Absolute Maximum Ratings\*," on page 82 for additional buffer information.

**Note:** Sink and source capabilities are dependant on the VDDVARIO voltage. Refer to Section 5.1, "Absolute Maximum Ratings\*," on page 82 for additional information.

# **Chapter 3 Functional Description**

This chapter provides functional descriptions of the various device features. These features have been categorized into the following sections:

- Auto-negotiation

- HP Auto-MDIX

- GMII Interface

- Serial Management Interface (SMI)

- Interrupt Management

- Resets

- Power-Down modes

- Configuration

- Miscellaneous Functions

- Application Diagrams

### 3.1 Auto-negotiation

The purpose of the auto-negotiation function is to automatically configure the PHY to the optimum link parameters based on the capabilities of its link partner. Auto-negotiation is a mechanism for exchanging configuration information between two link-partners and automatically selecting the highest performance mode of operation supported by both sides. Auto-negotiation is fully defined in clause 28 and clause 40 of the IEEE 802.3 specification.

Once auto-negotiation has completed, information about the resolved link can be passed back to the controller via the integrated Serial Management Interface (SMI). The results of the negotiation process are reflected in the Speed Indication field of the PHY Special Control / Status Register as well as the Auto Negotiation Link Partner Ability Register.

The advertised capabilities of the PHY are stored in Auto Negotiation Advertisement Register. The defaults advertised by the device are determined as described in Section 3.8.1.2.2, "Configuring the Mode of Operation (CONFIG[3:2])," on page 31.

The auto-negotiation protocol is a purely physical layer activity and proceeds independently of the MAC controller. When enabled, auto-negotiation is started by the occurrence of one of the following events:

- Hardware reset

- Software reset

- Power-down reset

- Link status down

- Setting the Restart Auto-Negotiate bit of the Basic Control Register

On detection of one of these events, the device begins auto-negotiation by transmitting bursts of Fast Link Pulses (FLP). The data transmitted by an FLP burst is known as a "Link Code Word." This exchange of information allows link partners to determine the Highest Common Ability (HCD).

Once a capability match has been determined, the link code words are repeated with the acknowledge bit set. Any difference in the main content of the link code words at this time will cause auto-negotiation to re-start. Auto-negotiation will also re-start if all of the required FLP bursts are not received.

Writing the 100BASE-TX Full Duplex, 100BASE-TX, 10BASE-T Full Duplex, and 10BASE-T bits of the Auto Negotiation Advertisement Register allows software control of the advertised capabilities.

However, writing the Auto Negotiation Advertisement Register does not automatically re-start autonegotiation. The Restart Auto-Negotiate bit of the Basic Control Register must be set before the new abilities will be advertised. Auto-negotiation can also be disabled via software by clearing the Auto-Negotiation Enable bit of the Basic Control Register.

Auto-Negotiation also resolves the Master/Slave clocking relationship between two PHYs for a 1000BASE-T link. Refer to Section 3.1.4, "Master/Slave," on page 20 for additional information.

### 3.1.1 Restarting Auto-negotiation

Auto-negotiation can be restarted at any time by using the Restart Auto-Negotiate bit of the Basic Control Register. Auto-negotiation will also re-start if the link is broken at any time. A broken link is caused by signal loss. This may occur because of a cable break, or because of an interruption in the signal transmitted by the Link Partner. Auto-negotiation resumes in an attempt to determine the new link configuration.

If the management entity restarts Auto-negotiation by writing to the Restart Auto-Negotiate bit, the device will respond by stopping all transmission/receiving operations. Auto-negotiation will restart after approximately 1200 mS. The Link Partner will have also dropped the link and will resume auto-negotiation.

### 3.1.2 Disabling Auto-negotiation

Auto-negotiation can be disabled via software by clearing the Auto-Negotiation Enable bit of the Basic Control Register. The device will then force its speed of operation to reflect the information in the Speed Select[1], Speed Select[0], and Duplex Mode bits of the Basic Control Register. These bits are ignored when auto-negotiation is enabled.

### 3.1.3 Parallel Detection

If the LAN8810/LAN8810i is connected to a device lacking the ability to auto-negotiate (i.e., no FLPs are detected), it is able to determine the speed of the link based on either 100M MLT-3 symbols or 10M Normal Link Pulses. In this case, the link is presumed to be half-duplex per the IEEE standard. This ability is known as "Parallel Detection". This feature ensures inter operability with legacy link partners.

The Ethernet MAC has access to information regarding parallel detect via the Auto Negotiation Expansion Register. If a link is formed via parallel detection, the Link Partner Auto-Negotiation Able bit of the Auto Negotiation Expansion Register is cleared to indicate that the Link Partner is not capable of auto-negotiation. If a fault occurs during parallel detection, the Parallel Detection Fault bit of this register is set.

The Auto Negotiation Link Partner Ability Register is updated with information from the link partner which is coded in the received FLPs. If the Link Partner is not auto-negotiation capable, then the Auto Negotiation Link Partner Ability Register is updated after completion of parallel detection to reflect the speed capability of the Link Partner.

Parallel detect cannot be used to establish Gigabit Ethernet links because echo cancellation and signal recovery on a Gigabit Ethernet link requires resolution of the Master/Slave clock relationship, which requires the exchange of FLPs.

#### 3.1.4 Master/Slave

In 1000BASE-T, one of the two link partner devices must be configured as Master and the other as Slave. The Master device transmits data using the local clock, while the Slave device uses the clock recovered from incoming data.

The Master and Slave assignments are set using the configuration pins as described in Section 3.8.1.2.2, "Configuring the Mode of Operation (CONFIG[3:2])," on page 31 or by using the Master/Slave Manual Config Enable and Master/Slave Manual Config Value bits of the Master/Slave

Control Register. If both the link partner and the local device are manually given the same Master/Slave assignment, an error will be indicated in the Master/Slave Configuration Fault bit of the Master/Slave Status Register.

Depending on the link partner configuration, the manual Master/Slave mode can be resolved to sixteen possible outcomes, as shown in Table 3.1.

Table 3.1 Master/Slave Resolution for 1000BASE-T

| LAN8810/LAN8810I<br>ADVERTISEMENT | LINK PARTNER<br>ADVERTISEMENT | LAN8810/LAN8810I RESULT     | LINK PARTNER RESULT         |

|-----------------------------------|-------------------------------|-----------------------------|-----------------------------|

| Single-Port                       | Single-Port                   | M/S resolved by random seed | M/S resolved by random seed |

| Single-Port                       | Multi-Port                    | Slave                       | Master                      |

| Single-Port                       | Manual Master                 | Slave                       | Master                      |

| Single-Port                       | Manual Slave                  | Master                      | Slave                       |

| Multi-Port                        | Single-Port                   | Master                      | Slave                       |

| Multi-Port                        | Multi-Port                    | M/S resolved by random seed | M/S resolved by random seed |

| Multi-Port                        | Manual Master                 | Slave                       | Master                      |

| Multi-Port                        | Manual Slave                  | Master                      | Slave                       |

| Manual Master                     | Single-Port                   | Master                      | Slave                       |

| Manual Master                     | Multi-Port                    | Master                      | Slave                       |

| Manual Master                     | Manual Master                 | No Link                     | No Link                     |

| Manual Master                     | Manual Slave                  | Master                      | Slave                       |

| Manual Slave                      | Single-Port                   | Slave                       | Master                      |

| Manual Slave                      | Multi-Port                    | Slave                       | Master                      |

| Manual Slave                      | Manual Master                 | Slave                       | Master                      |

| Manual Slave                      | Manual Slave                  | No Link                     | No Link                     |

### 3.1.5 Manual Operation

The device supports a manual (forced) operation for test purposes. In manual operation, the user sets the link speed (10Mbps or 100Mbps) and the duplex state (full or half).

Auto-negotiation must be disabled in order to manually configure the speed and the duplex. This may be accomplished using the configuration pins, as described in Section 3.8.1.2.2, "Configuring the Mode of Operation (CONFIG[3:2])," on page 31, or by using the Basic Control Register register as described in Section 3.1.2, "Disabling Auto-negotiation," on page 20. For 10BASE-T and 100BASE-TX, the link state of the device is determined by the Speed Select[1], Speed Select[0], and Duplex Mode bits of the Basic Control Register. Manual operation at a link speed of 1000Mbps is not supported.

### 3.1.6 Half vs. Full-Duplex

Half-duplex operation relies on the CSMA/CD (Carrier Sense Multiple Access / Collision Detect) protocol to handle network traffic and collisions. In this mode, the internal carrier sense signal, CRS, responds to both transmit and receive activity. If data is received while the PHY is transmitting, a collision results.

In full-duplex mode, the PHY is able to transmit and receive data simultaneously and collision detection is disabled. In this mode, the internal CRS responds only to receive activity. In 10BASE-T and 100BASE-T mode, CRS is redefined to respond only to received activity. In 1000BASE-T, CRS is disabled.

Table 3.2 describes the behavior of the internal CRS bit under all receive/transmit conditions.

Table 3.2 CRS Behavior

| MODE             | SPEED    | DUPLEX      | ACTIVITY     | CRS BEHAVIOR<br>(Note 3.1) |

|------------------|----------|-------------|--------------|----------------------------|

| Manual           | 10 Mbps  | Half-Duplex | Transmitting | Active                     |

| Manual           | 10 Mbps  | Half-Duplex | Receiving    | Active                     |

| Manual           | 10 Mbps  | Full-Duplex | Transmitting | Low                        |

| Manual           | 10 Mbps  | Full-Duplex | Receiving    | Active                     |

| Manual           | 100 Mbps | Half-Duplex | Transmitting | Active                     |

| Manual           | 100 Mbps | Half-Duplex | Receiving    | Active                     |

| Manual           | 100 Mbps | Full-Duplex | Transmitting | Low                        |

| Manual           | 100 Mbps | Full-Duplex | Receiving    | Active                     |

| Auto-Negotiation | 10 Mbps  | Half-Duplex | Transmitting | Active                     |

| Auto-Negotiation | 10 Mbps  | Half-Duplex | Receiving    | Active                     |

| Auto-Negotiation | 10 Mbps  | Full-Duplex | Transmitting | Low                        |

| Auto-Negotiation | 10 Mbps  | Full-Duplex | Receiving    | Active                     |

| Auto-Negotiation | 100 Mbps | Half-Duplex | Transmitting | Active                     |

| Auto-Negotiation | 100 Mbps | Half-Duplex | Receiving    | Active                     |

| Auto-Negotiation | 100 Mbps | Full-Duplex | Transmitting | Low                        |

| Auto-Negotiation | 100 Mbps | Full-Duplex | Receiving    | Active                     |

Note 3.1 The internal CRS signal operates in two modes: Active and Low. When in Active mode, the internal CRS will transition high and low upon line activity, where a high value indicates a carrier has been detected. In Low mode, the internal CRS stays low and does not indicate carrier detection.

### 3.2 HP Auto-MDIX

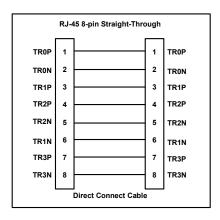

HP Auto-MDIX facilitates the use of CAT-5 (100BASE-T) media UTP interconnect cable without consideration of interface wiring scheme. If a user plugs in either a direct connect LAN cable, or a cross-over patch cable, as shown in Figure 3.1, the Auto-MDIX PHY is capable of configuring the twisted pair pins for correct transceiver operation.

The internal logic of the device detects the TX and RX pins of the connecting device. It can automatically re-assign channel 0 and 1 if required to establish a link. In 1000BASE-T mode, it can reassign channel 2 and 3. Crossover resolution precedes the actual auto-negotiation process that involves exchange of FLPs to advertise capabilities. Automatic MDI/MDIX is described in IEEE 802.3ab Clause 40, section 40.8.2. Since the RX and TX line pairs are interchangeable, special PCB design

considerations are needed to accommodate the symmetrical magnetics and termination of an Auto-MDIX design.

Auto-MDIX is enabled by default, and can be disabled by the Auto MDIX Disable bit in the 10/100 Mode Control/Status Register. When Auto-MDIX is disabled, the TX and RX pins can be configured manually by the MDI/MDI-X 0:1 and MDI/MDI-X 2:3 bits in the Extended Mode Control/Status Register.

The device includes an advanced crossover resolution capability called Semi Crossover. This is an extension to HP Auto-MDIX that corrects for a cable with only two pairs crossed. If Semi Crossover is enabled, after the device has attempted to establish a link with all four signal pairs normal or crossed, it will attempt to establish a link with pairs 2/3 switched and 0/1 straight, and then with pairs 0/1 switched and pairs 2/3 straight. The Semi Crossover is enabled by default, and can be disabled by the Semi Crossover Enable bit in the 10/100 Mode Control/Status Register.

After resolution of crossed pairs is complete, using either HP Auto-MDIX or the Semi Crossover function, the MDI/MDI-X status is reported through the XOVER Resolution 0:1 and XOVER Resolution 2:3 bits of the User Status 2 Register.

Figure 3.1 Cable Connection Types: Straight-Through, Crossover, Semi Crossover

### 3.2.1 Required Ethernet Magnetics

The magnetics selected for use with the device should be an Auto-MDIX style magnetic available from several vendors. Refer to SMSC Application Note 8.13 "Suggested Magnetics" for the latest qualified and suggested magnetics. Vendors and part numbers are provided in this application note.

### 3.3 GMII Interface

The device communicates with an external MAC using the Gigabit Media Independent Interface (GMII). The GMII is compliant with the IEEE 802.3 standard, and provides support for 1000BASE-T, 100BASE-TX, or 10BASE-T operation.

For 1000BASE-T, the MAC generated 125MHz GTXCLK transmit clock is used to synchronize the TXD, TXEN and TXER signals. For 100BASE-TX and 10BASE-T operation, the device generated TXCLK transmit clock is used to synchronize the TXD, TXEN and TXER signals. TXCLK is 25MHz or 2.5MHz for 100BASE-TX and 10BASE-T operation, respectively. TXER and TXEN are both driven by the MAC and indicate a transmit error and valid transmit data, respectively. On the receiver side, the device generated RXCLK is used to synchronize the RXD, RXDV, RXER, COL and CRS signals for all modes of operation.

The GMII provides backwards compatibility with the legacy MII. Table 3.3, "GMII/MII Signal Mapping" describes which pins are used in each mode.

**GMII MODE** MII MODE (IEEE 802.3 CLAUSE 35) (IEEE 802.3 CLAUSE 22) TXD[3:0] TXD[3:0] TXD[7:4] **TXFN TXEN TXER TXER** TXCLK (10/100Mbps operation) **TXCLK** GTXCLK (1000Mbps operation) COL COL **CRS CRS** RXD[3:0] RXD[3:0] RXD[7:4] **RXDV RXDV RXER RXER RXCLK RXCLK**

Table 3.3 GMII/MII Signal Mapping

Timing information for the GMII/MII interface is provided in Section 5.5, "AC Specifications," on page 87. For additional information on the GMII/MII interface, refer to the IEEE 802.3 specification.

### 3.3.1 MII Isolate Mode

The device may be configured to electrically isolate the GMII pins by setting the Isolate bit of the Basic Control Register. In this mode, all MAC data interface output pins are HIGH and all MAC data interface input pins are ignored. In this mode, the SMI interface is kept active, allowing the MAC to access the SMI registers and generate interrupts. All MDI operations are halted while in isolate mode.

### 3.4 Serial Management Interface (SMI)

The Serial Management Interface is used to control the device and obtain its status. This interface supports the standard PHY registers required by Clause 22 of the 802.3 standard, as well as "vendor-specific" registers allowed by the specification. Non-supported registers (such as 11 to 14) will be read as hexadecimal "FFFF". Device registers are detailed in Chapter 4, "Register Descriptions," on page 43.

At the system level, SMI provides 2 signals: MDIO and MDC. The MDC signal is an aperiodic clock provided by the station management controller (SMC). MDIO is a bi-directional data SMI input/output signal that receives serial data (commands) from the controller SMC and sends serial data (status) to the SMC. The minimum time between edges of the MDC is 160 ns. There is no maximum time between edges. The minimum cycle time (time between two consecutive rising or two consecutive falling edges) is 400 ns. These modest timing requirements allow this interface to be easily driven by the I/O port of a microcontroller.

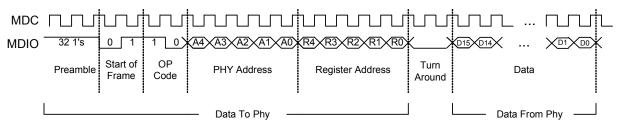

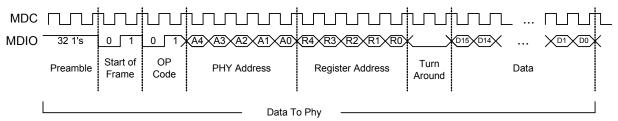

The data on the MDIO line is latched on the rising edge of the MDC. The frame structure and timing of the data is shown in Figure 3.1 and Figure 3.2. The timing relationships of the MDIO signals are further described in Section 5.5.7, "SMI Timing," on page 95.

### Read Cycle

Figure 3.1 MDIO Timing and Frame Structure - READ Cycle

# Write Cycle

Figure 3.2 MDIO Timing and Frame Structure - WRITE Cycle

### 3.5 Interrupt Management

The device supports multiple interrupt capabilities which are not a part of the IEEE 802.3 specification. An active low asynchronous interrupt signal may be generated on the IRQ pin when selected events are detected, as configured by the Interrupt Mask Register.

To set an interrupt, the corresponding mask bit in the Interrupt Mask Register must be set (see Table 3.4). When the associated event occurs, the IRQ pin will be asserted. When the corresponding event to deassert IRQ is true, the IRQ pin will be deasserted. All interrupts are masked following a reset

**Note:** Table 3.4 utilizes register index and bit number referencing in lieu of individual names. For example, "30.10" is used to reference bit 10 (transmitter elastic buffer overflow interrupt enable) of the Interrupt Mask Register (register index 30).

**Table 3.4 Interrupt Management Table**

| MASK     | INTERRUPT SOURCE FLAG |                                         | TERRUPT SOURCE FLAG INTERRUPT SOURCE |                             | EVENT TO<br>ASSERT IRQ                  | EVENT TO<br>DEASSERT IRQ                                                                                  |

|----------|-----------------------|-----------------------------------------|--------------------------------------|-----------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------|

| 30.15:11 | 29.15:11              | RESERVED                                | -NA-                                 | -NA-                        | -NA-                                    | -NA-                                                                                                      |

| 30.10    | 29.10                 | Transmitter Elastic<br>Buffer Overflow  | -NA-                                 | -NA-<br>(Note 3.3)          | Transmitter Elastic<br>Buffer Overflow  | Overflow condition resolved                                                                               |

| 30.9     | 29.9                  | Transmitter Elastic<br>Buffer Underflow | -NA-                                 | -NA-<br>(Note 3.3)          | Transmitter Elastic<br>Buffer Underflow | Underflow condition resolved                                                                              |

| 30.8     | 29.8                  | Idle Error Count<br>Overflow            | 10.7:0                               | Idle Error Count            | Idle Error Count<br>Overflow            | Reading register 10                                                                                       |

| 30.7     | 29.7                  | ENERGYON                                | 17.1                                 | ENERGYON                    | Rising 17.1<br>(Note 3.2)               | Falling 17.1 or<br>Reading register 29                                                                    |

| 30.6     | 29.6                  | Auto-Negotiation complete               | 1.5                                  | Auto-Negotiate<br>Complete  | Rising 1.5                              | Falling 1.5 or<br>Reading register 29                                                                     |

| 30.5     | 29.5                  | Remote Fault<br>Detected                | 1.4                                  | Remote Fault                | Rising 1.4                              | Falling 1.4, or<br>Reading register 1 or<br>Reading register 29                                           |

| 30.4     | 29.4                  | Link Down                               | 1.2                                  | Link Status                 | Falling 1.2                             | Reading register 1 or<br>Reading register 29                                                              |

| 30.3     | 29.3                  | RESERVED                                | -NA-                                 | -NA-                        | -NA-                                    | -NA-                                                                                                      |