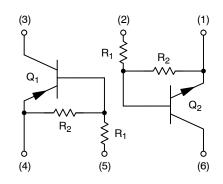

### Complementary Bias Resistor Transistors R1 = 22 k $\Omega$ , R2 = 47 k $\Omega$

# NPN and PNP Transistors with Monolithic Bias Resistor Network

This series of digital transistors is designed to replace a single device and its external resistor bias network. The Bias Resistor Transistor (BRT) contains a single transistor with a monolithic bias network consisting of two resistors; a series base resistor and a base-emitter resistor. The BRT eliminates these individual components by integrating them into a single device. The use of a BRT can reduce both system cost and board space.

#### **Features**

- Simplifies Circuit Design

- Reduces Board Space

- Reduces Component Count

- S and NSV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q101 Qualified and PPAP Capable\*

- These Devices are Pb-Free, Halogen Free/BFR Free and are RoHS Compliant

### **MAXIMUM RATINGS**

$(T_A = 25^{\circ}C \text{ both polarities } Q_1 \text{ (PNP) } \& Q_2 \text{ (NPN)}, \text{ unless otherwise noted)}$

| Rating                         | Symbol               | Max | Unit |

|--------------------------------|----------------------|-----|------|

| Collector-Base Voltage         | V <sub>CBO</sub>     | 50  | Vdc  |

| Collector-Emitter Voltage      | $V_{CEO}$            | 50  | Vdc  |

| Collector Current - Continuous | Ic                   | 100 | mAdc |

| Input Forward Voltage          | V <sub>IN(fwd)</sub> | 40  | Vdc  |

| Input Reverse Voltage          | V <sub>IN(rev)</sub> | 7   | Vdc  |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

### **ORDERING INFORMATION**

| Device                                  | Package | Shipping <sup>†</sup> |

|-----------------------------------------|---------|-----------------------|

| MUN5334DW1T1G,<br>NSVMUN5334DW1T1G*     | SOT-363 | 3,000/Tape & Reel     |

| NSBC124XPDXV6T1G,<br>NSVBC124XPDXV6T1G* | SOT-563 | 4,000/Tape & Reel     |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

### ON Semiconductor®

www.onsemi.com

### **PIN CONNECTIONS**

### **MARKING DIAGRAMS**

SOT-363 CASE 419B

SOT-563 CASE 463A

34 = Specific Device Code

M = Date Code\*

■ Pb-Free Package

(Note: Microdot may be in either location)

<sup>\*</sup>Date Code orientation may vary depending upon manufacturing location.

### THERMAL CHARACTERISTICS

|                                                                                                                   | Characteristic               | Symbol                            | Max                      | Unit        |

|-------------------------------------------------------------------------------------------------------------------|------------------------------|-----------------------------------|--------------------------|-------------|

| MUN5334DW1 (SOT-363) ONE J                                                                                        | JUNCTION HEATED              | •                                 |                          |             |

| Total Device Dissipation  T <sub>A</sub> = 25°C (Note 1)  (Note 2)  Derate above 25°C (Note 2)                    | lote 1)                      | P <sub>D</sub>                    | 187<br>256<br>1.5<br>2.0 | mW<br>mW/°C |

|                                                                                                                   | ote 1)<br>lote 2)            | $R_{	hetaJA}$                     | 670<br>490               | °C/W        |

| MUN5334DW1 (SOT-363) BOTH                                                                                         | JUNCTION HEATED (Note 3)     |                                   |                          |             |

| Total Device Dissipation $T_A = 25^{\circ}C \qquad \text{(Note 1)}$ $\text{(Note 2)}$ Derate above 25°C  (Note 2) | lote 1)                      | P <sub>D</sub>                    | 250<br>385<br>2.0<br>3.0 | mW<br>mW/°C |

| Thermal Resistance,<br>Junction to Ambient (Note 2)                                                               | lote 1)                      | $R_{	heta JA}$                    | 493<br>325               | °C/W        |

| Thermal Resistance,<br>Junction to Lead (Note 1)<br>(Note 2)                                                      |                              | $R_{	heta JL}$                    | 188<br>208               | °C/W        |

| Junction and Storage Temperatur                                                                                   | re Range                     | T <sub>J</sub> , T <sub>stg</sub> | -55 to +150              | °C          |

| NSBC124XPDXV6 (SOT-563) OF                                                                                        | NE JUNCTION HEATED           |                                   |                          |             |

| Total Device Dissipation  T <sub>A</sub> = 25°C (Note 1)  Derate above 25°C (N                                    | lote 1)                      | P <sub>D</sub>                    | 357<br>2.9               | mW<br>mW/°C |

| Thermal Resistance,<br>Junction to Ambient (N                                                                     | lote 1)                      | $R_{\theta JA}$                   | 350                      | °C/W        |

| NSBC124XPDXV6 (SOT-563) BC                                                                                        | OTH JUNCTION HEATED (Note 3) |                                   |                          |             |

| Total Device Dissipation T <sub>A</sub> = 25°C (Note 1) Derate above 25°C (N                                      | lote 1)                      | P <sub>D</sub>                    | 500<br>4.0               | mW<br>mW/°C |

| Thermal Resistance,<br>Junction to Ambient (N                                                                     | lote 1)                      | $R_{	heta JA}$                    | 250                      | °C/W        |

| Junction and Storage Temperatur                                                                                   | re Range                     | T <sub>J</sub> , T <sub>stg</sub> | -55 to +150              | °C          |

FR-4 @ Minimum Pad.

FR-4 @ 1.0 × 1.0 Inch Pad.

Both junction heated values assume total power is sum of two equally powered channels.

**ELECTRICAL CHARACTERISTICS** (T<sub>A</sub> = 25°C both polarities Q<sub>1</sub> (PNP) & Q<sub>2</sub> (NPN), unless otherwise noted)

| Characteristic                                                                                                                                          | Symbol                         | Min    | Тур        | Max    | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------|------------|--------|------|

| OFF CHARACTERISTICS                                                                                                                                     |                                |        |            | •      | •    |

| Collector-Base Cutoff Current $(V_{CB} = 50 \text{ V, } I_{E} = 0)$                                                                                     | I <sub>CBO</sub>               | -      | -          | 100    | nAdc |

| Collector-Emitter Cutoff Current (V <sub>CE</sub> = 50 V, I <sub>B</sub> = 0)                                                                           | I <sub>CEO</sub>               | -      | -          | 500    | nAdc |

| Emitter-Base Cutoff Current $(V_{EB} = 6.0 \text{ V}, I_{C} = 0)$                                                                                       | I <sub>EBO</sub>               | -      | -          | 0.13   | mAdc |

| Collector-Base Breakdown Voltage ( $I_C = 10 \mu A, I_E = 0$ )                                                                                          | V <sub>(BR)CBO</sub>           | 50     | -          | -      | Vdc  |

| Collector-Emitter Breakdown Voltage (Note 4) (I <sub>C</sub> = 2.0 mA, I <sub>B</sub> = 0)                                                              | V <sub>(BR)CEO</sub>           | 50     | -          | -      | Vdc  |

| ON CHARACTERISTICS                                                                                                                                      |                                |        |            |        |      |

| DC Current Gain (Note 4)<br>(I <sub>C</sub> = 5.0 mA, V <sub>CE</sub> = 10 V)                                                                           | h <sub>FE</sub>                | 80     | 150        | -      |      |

| Collector-Emitter Saturation Voltage (Note 4) (I <sub>C</sub> = 10 mA, I <sub>B</sub> = 1.0 mA)                                                         | V <sub>CE(sat)</sub>           | _      | _          | 0.25   | V    |

| Input Voltage (Off) ( $V_{CE} = 5.0 \text{ V}, I_{C} = 100 \mu\text{A}$ ) (NPN) ( $V_{CE} = 5.0 \text{ V}, I_{C} = 100 \mu\text{A}$ ) (PNP)             | V <sub>i(off)</sub>            |        | 0.8<br>0.9 | -<br>- | Vdc  |

| Input Voltage (On) $(V_{CE} = 0.2 \text{ V, } I_{C} = 3.0 \text{ mA}) \text{ (NPN)} $ $(V_{CE} = 0.2 \text{ V, } I_{C} = 3.0 \text{ mA}) \text{ (PNP)}$ | V <sub>i(on)</sub>             | -<br>- | 1.3<br>1.3 | _<br>_ | Vdc  |

| Output Voltage (On) ( $V_{CC} = 5.0 \text{ V}, V_B = 2.5 \text{ V}, R_L = 1.0 \text{ k}\Omega$ )                                                        | V <sub>OL</sub>                | -      | -          | 0.2    | Vdc  |

| Output Voltage (Off) $(V_{CC} = 5.0 \text{ V}, V_B = 0.5 \text{ V}, R_L = 1.0 \text{ k}\Omega)$                                                         | V <sub>OH</sub>                | 4.9    | -          | -      | Vdc  |

| Input Resistor                                                                                                                                          | R1                             | 15.4   | 22         | 28.6   | kΩ   |

| Resistor Ratio                                                                                                                                          | R <sub>1</sub> /R <sub>2</sub> | 0.38   | 0.47       | 0.56   |      |

<sup>4.</sup> Pulsed Condition: Pulse Width = 300 ms, Duty Cycle ≤ 2%.

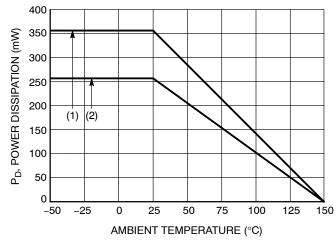

(1) SOT–363; 1.0  $\times$  1.0 Inch Pad (2) SOT–563; Minimum Pad

Figure 1. Derating Curve

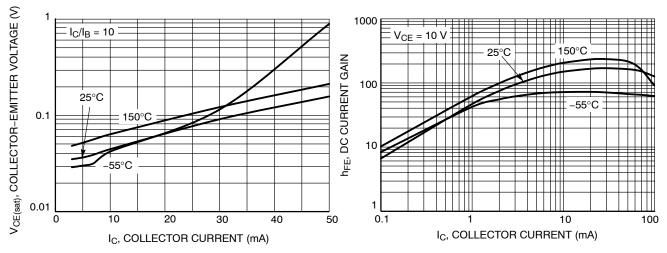

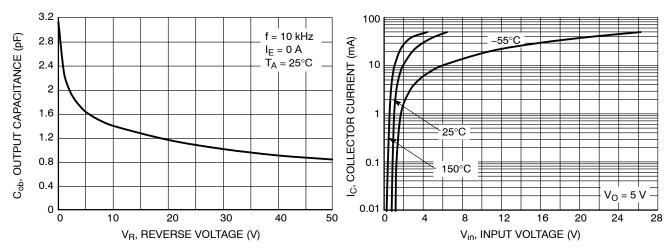

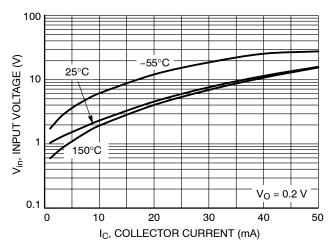

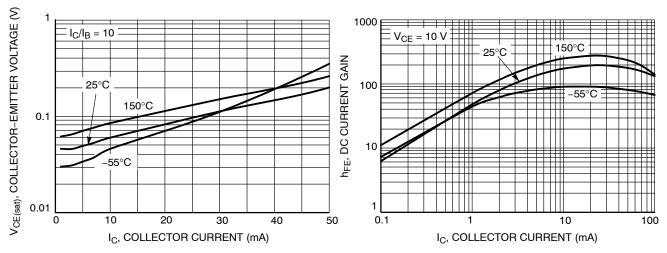

## TYPICAL CHARACTERISTICS – NPN TRANSISTOR MUN5334DW1, NSBC124XPDXV6

Figure 2. V<sub>CE(sat)</sub> vs. I<sub>C</sub>

Figure 3. DC Current Gain

Figure 4. Output Capacitance

Figure 5. Output Current vs. Input Voltage

Figure 6. Input Voltage vs. Output Current

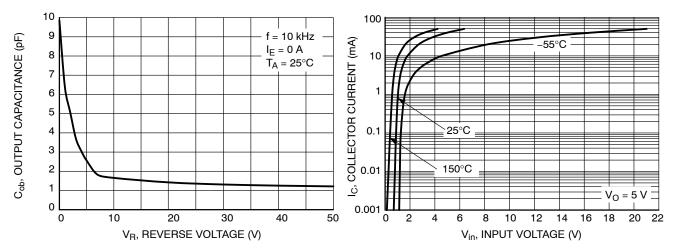

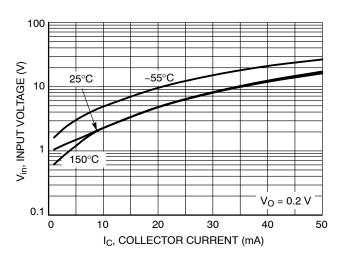

## TYPICAL CHARACTERISTICS – PNP TRANSISTOR MUN5334DW1, NSBC124XPDXV6

Figure 7. V<sub>CE(sat)</sub> vs. I<sub>C</sub>

Figure 8. DC Current Gain

Figure 9. Output Capacitance

Figure 10. Output Current vs. Input Voltage

Figure 11. Input Voltage vs. Output Current

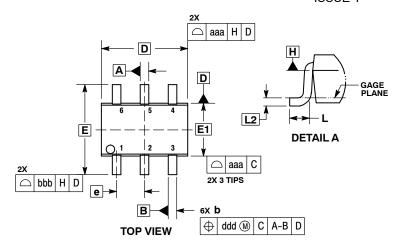

### PACKAGE DIMENSIONS

### SC-88/SC70-6/SOT-363

CASE 419B-02 **ISSUE Y**

#### NOTES:

- ITES:

DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

CONTROLLING DIMENSION: MILLIMETERS.

DIMENSIONS D AND E1 DO NOT INCLUDE MOLD FLASH,

PROTRUSIONS, OR GATE BURRS. MOLD FLASH, PROTRUSIONS, OR GATE BURRS SHALL NOT EXCEED 0.20 PER END.

DIMENSIONS D AND E1 AT THE OUTERMOST EXTREMES OF

THE PLASTIC BODY AND DATUM H.

DATUMS A AND B ARE DETERMINED AT DATUM H.

DIMENSIONS B AND c APPLY TO THE FLAT SECTION OF THE

LEAD BETWEEN 0.08 AND 0.15 FROM THE TIP.

DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION.

ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 TOTAL IN

- ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 TOTAL IN EXCESS OF DIMENSION b AT MAXIMUM MATERIAL CONDI-TION. THE DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OF THE FOOT.

|     | MILLIMETERS |      |      | INCHES |          |       |

|-----|-------------|------|------|--------|----------|-------|

| DIM | MIN         | NOM  | MAX  | MIN    | NOM      | MAX   |

| Α   |             |      | 1.10 |        |          | 0.043 |

| A1  | 0.00        |      | 0.10 | 0.000  |          | 0.004 |

| A2  | 0.70        | 0.90 | 1.00 | 0.027  | 0.035    | 0.039 |

| b   | 0.15        | 0.20 | 0.25 | 0.006  | 0.008    | 0.010 |

| С   | 0.08        | 0.15 | 0.22 | 0.003  | 0.006    | 0.009 |

| D   | 1.80        | 2.00 | 2.20 | 0.070  | 0.078    | 0.086 |

| E   | 2.00        | 2.10 | 2.20 | 0.078  | 0.082    | 0.086 |

| E1  | 1.15        | 1.25 | 1.35 | 0.045  | 0.049    | 0.053 |

| е   | 0.65 BSC    |      |      | 0      | .026 BS  | С     |

| L   | 0.26        | 0.36 | 0.46 | 0.010  | 0.014    | 0.018 |

| L2  | 0.15 BSC    |      |      | (      | 0.006 BS | SC    |

| aaa | 0.15        |      |      |        | 0.006    |       |

| bbb | 0.30        |      |      | 0.012  |          |       |

| ccc | 0.10        |      |      | 0.004  |          |       |

| ddd | 0.10 0.004  |      |      |        |          |       |

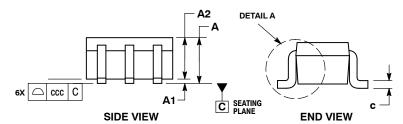

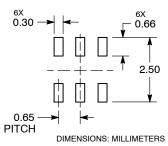

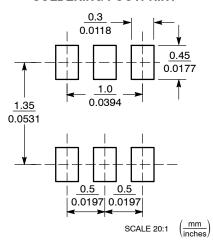

### **RECOMMENDED SOLDERING FOOTPRINT\***

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

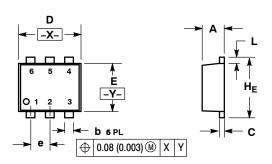

### PACKAGE DIMENSIONS

### SOT-563, 6 LEAD CASE 463A **ISSUE G**

- 1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

- TH-SWI, 1982.

CONTROLLING DIMENSION: MILLIMETERS

MAXIMUM LEAD THICKNESS INCLUDES LEAD

FINISH THICKNESS. MINIMUM LEAD THICKNESS

IS THE MINIMUM THICKNESS OF BASE MATERIAL.

|     | MILLIMETERS |      |      | INCHES   |       |       |

|-----|-------------|------|------|----------|-------|-------|

| DIM | MIN         | NOM  | MAX  | MIN      | NOM   | MAX   |

| Α   | 0.50        | 0.55 | 0.60 | 0.020    | 0.021 | 0.023 |

| b   | 0.17        | 0.22 | 0.27 | 0.007    | 0.009 | 0.011 |

| C   | 0.08        | 0.12 | 0.18 | 0.003    | 0.005 | 0.007 |

| D   | 1.50        | 1.60 | 1.70 | 0.059    | 0.062 | 0.066 |

| Е   | 1.10        | 1.20 | 1.30 | 0.043    | 0.047 | 0.051 |

| е   | 0.5 BSC     |      |      | 0.02 BSC |       |       |

| L   | 0.10        | 0.20 | 0.30 | 0.004    | 0.008 | 0.012 |

| HE  | 1.50        | 1.60 | 1.70 | 0.059    | 0.062 | 0.066 |

### **SOLDERING FOOTPRINT\***

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and the (III) are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries. SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA **Phone**: 303–675–2175 or 800–344–3860 Toll Free USA/Canada **Fax**: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center

Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

### **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

**ON Semiconductor:**

MUN5334DW1T1G NSVMUN5334DW1T1G